The reasoning layer for the

sovereign industrial

stack.

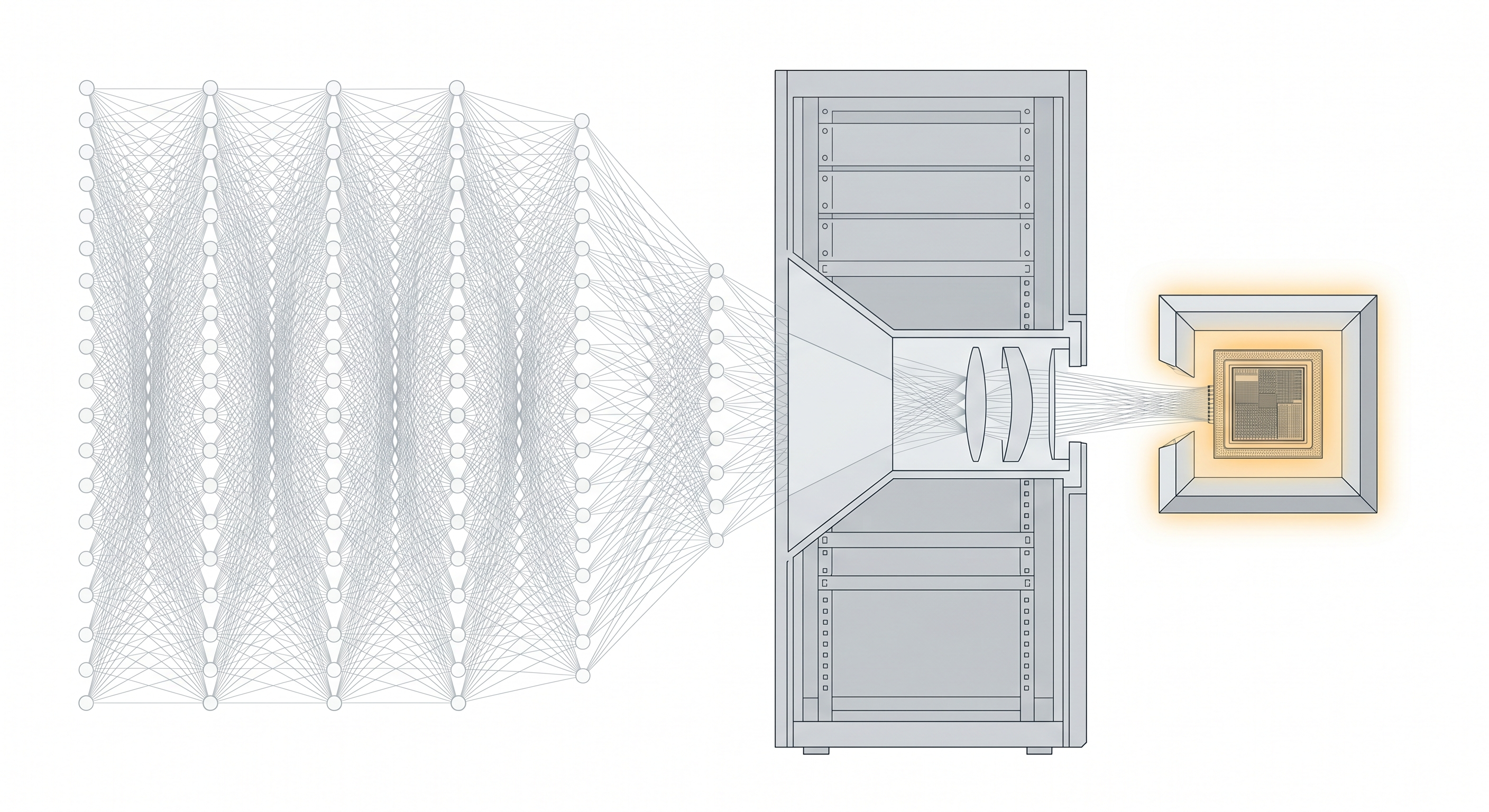

VoidSense is the AI-native reasoning system for the physical economy — a self-improving, air-gapped platform that turns every factory line into a closed loop between the atoms on the floor and the bits in the design. Purpose-built where general-purpose AI cannot go.

The logic of physical AI.

Autonomous manufacturing is a trillion-dollar market gated by a single bottleneck: the data doesn't exist. General-purpose AI will never cross the gap. VoidSense builds the substrate that does — and owns the distribution it's trained on.

The physical economy is starved of training data.

Manufacturing data is scarce, noisy, and historical — locked inside obsolete components, legacy assemblies, and fab-notes the line was never built to expose. Every incumbent inspection vendor ships the same blind spot.

Frontier models, trained on the open web, cannot learn what the factory floor refuses to publish. The gap isn't capability. It's ground truth — and it will not close on its own.

We manufacture the ground truth ourselves.

VoidSense runs a Physical Twin Simulation that generates physics-grounded data at a scale the real world can't — a proprietary corpus that compounds with every customer and cannot be replicated by a general-purpose lab.

A defect is reported only when physics says it's possible. Zero hallucination. Zero hand-wave. A durable moat, by construction.

A stack competitors can't assemble.

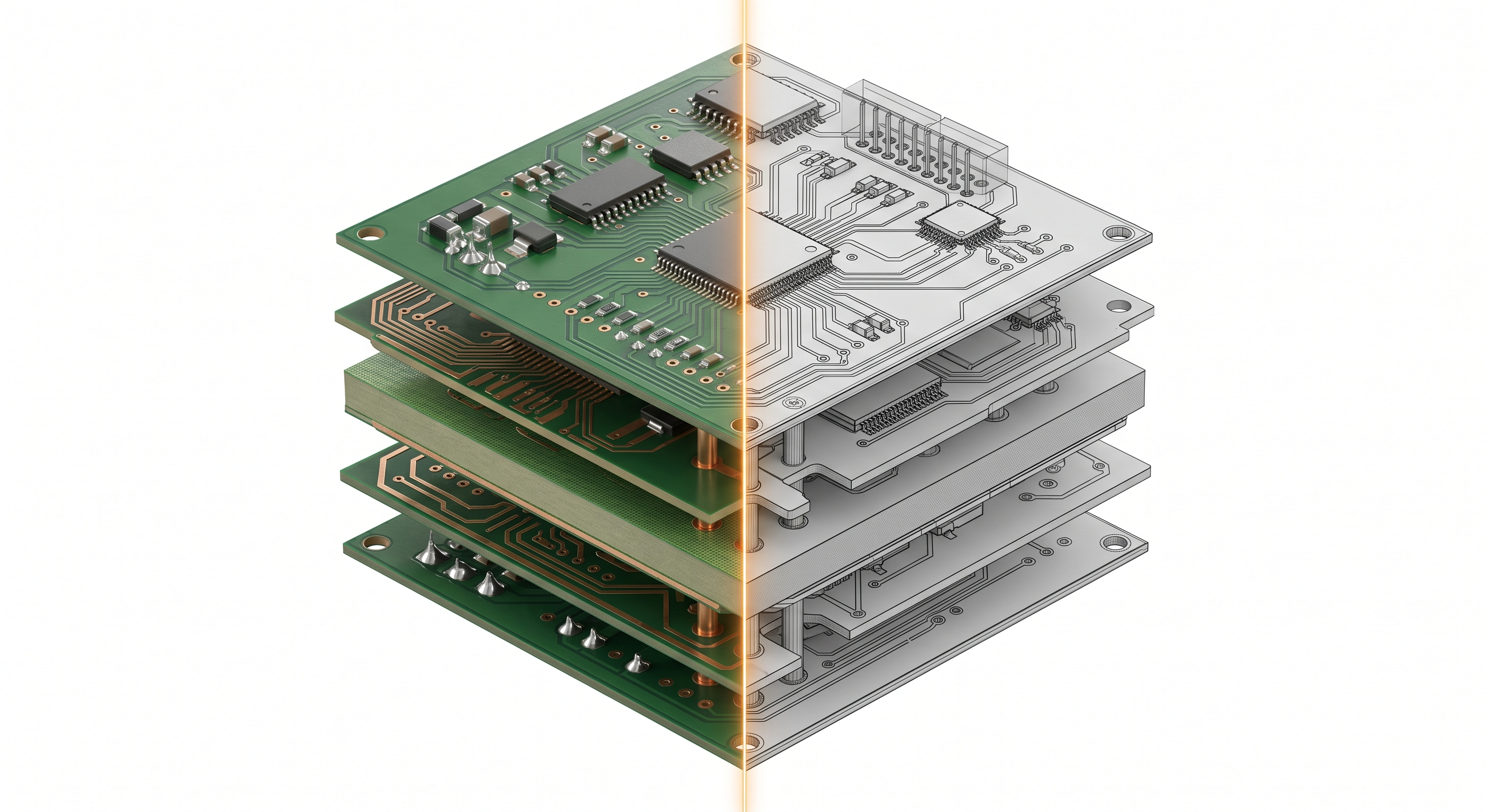

Four components, each defensible on its own; together they compound into a reasoning loop between design intent, physical dynamics, and field deployment. Every layer earns its place against a measured baseline.

The data moat competitors cannot buy.

Our synthetic foundry produces the defect corpus the physical economy refuses to expose — distribution-matched, physics-grounded, and fully owned. It is the substrate under every capability we ship, and it compounds with every customer line we deploy.

A reasoning core specialized on our own corpus.

An open-weight base, retrained on the Foundry's data, holds entire multi-modal project trees — CAD, netlists, fab-notes — in active memory. Every capability we ship is earned against a measured baseline, never presumed.

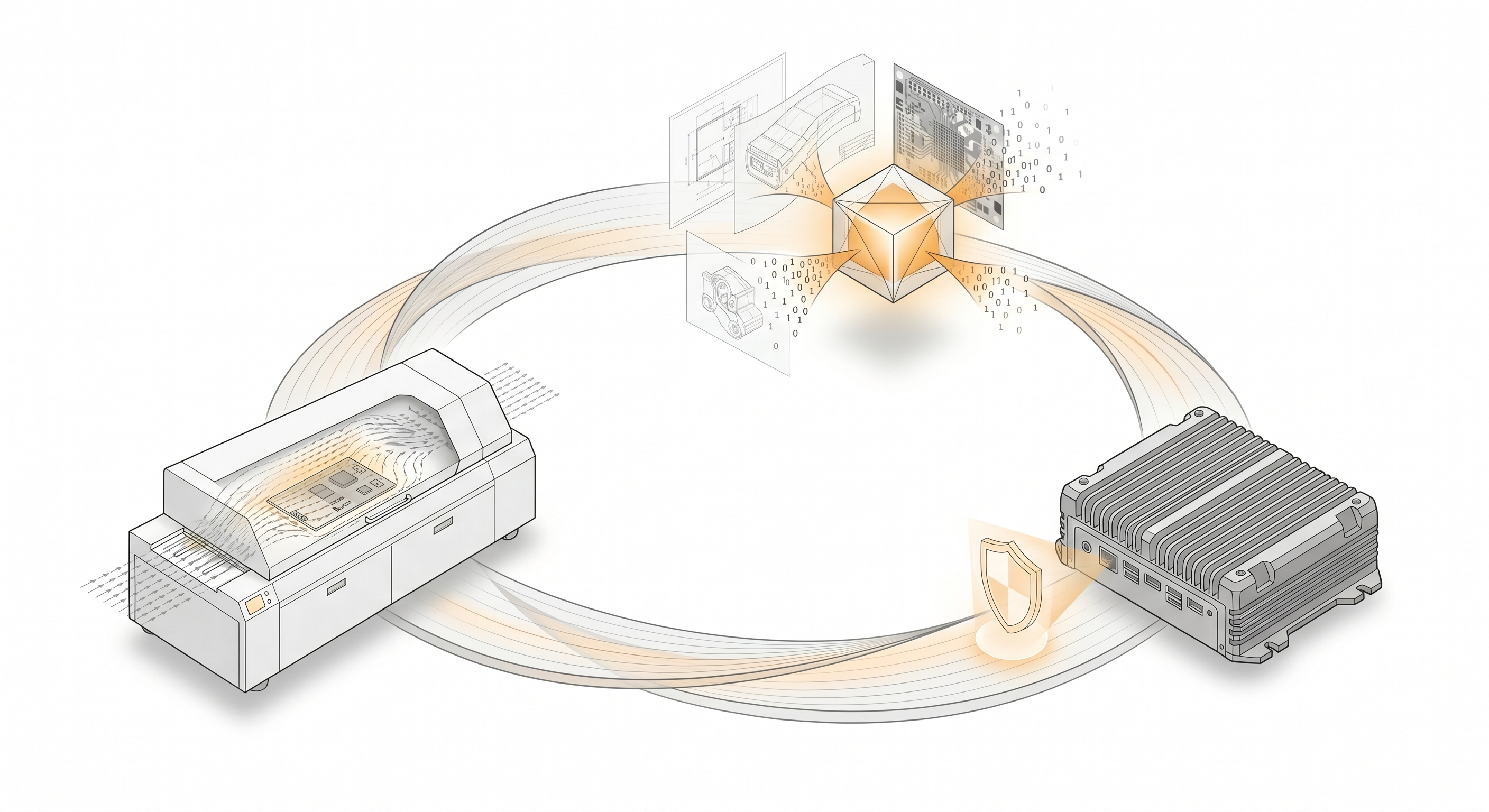

Zero-hallucination by architecture, not by prompt.

A neuro-symbolic grounding layer verifies every response against the deterministic topology of the customer's own project. A defect is reported only when the design logic says it's possible — the feature enterprise buyers refuse to ship without.

A system that gets sharper every day it runs.

A defect-injection self-improvement loop hardens the model against adversarial cases generated in the Foundry. Each release must clear an empirical gate before it ships — and our unit economics improve with every line we deploy, widening the gap against any general-purpose competitor.

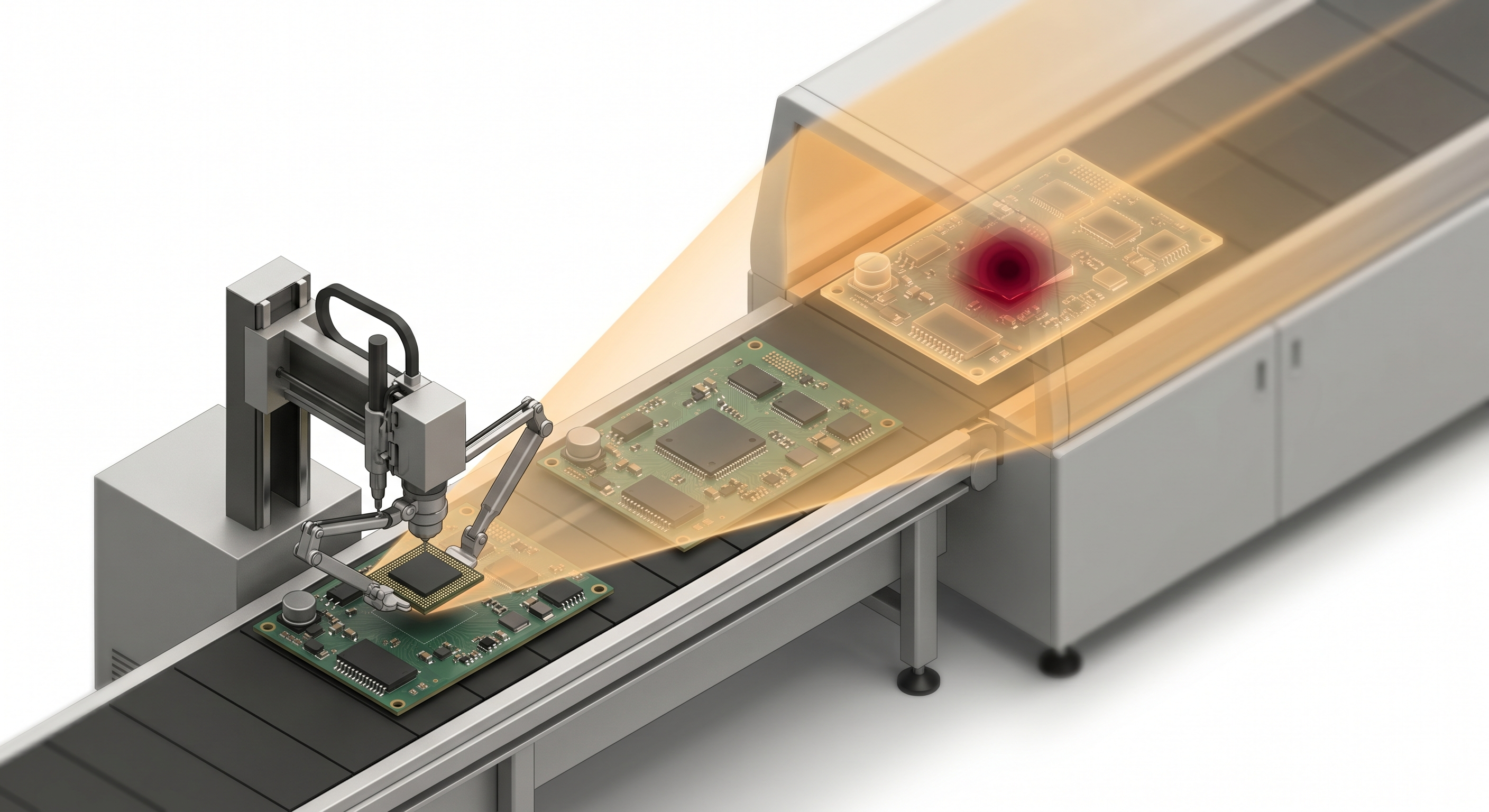

The wedge: a reconciliation problem every PCBA line has.

New Product Introduction burns 5–7 manual design-to-fab cycles because no tool reconciles unstructured fab-notes with structured CAD. We collapse the loop to 2–3 — and earn a beachhead in every PCBA line in the world.

From 5–7 cycles to 2–3.

By aligning unstructured PDF fab-notes with structured Gerber and AXI data, VoidSense collapses NPI cycles from 5–7 rounds to 2–3 — and, on the open PCBA-Reasoning-Bench (arXiv:2601.19222), doubles the accuracy of every general-purpose model tested. Real customer ROI, verifiable benchmark, measurable in weeks.

Defects no single sensor can see.

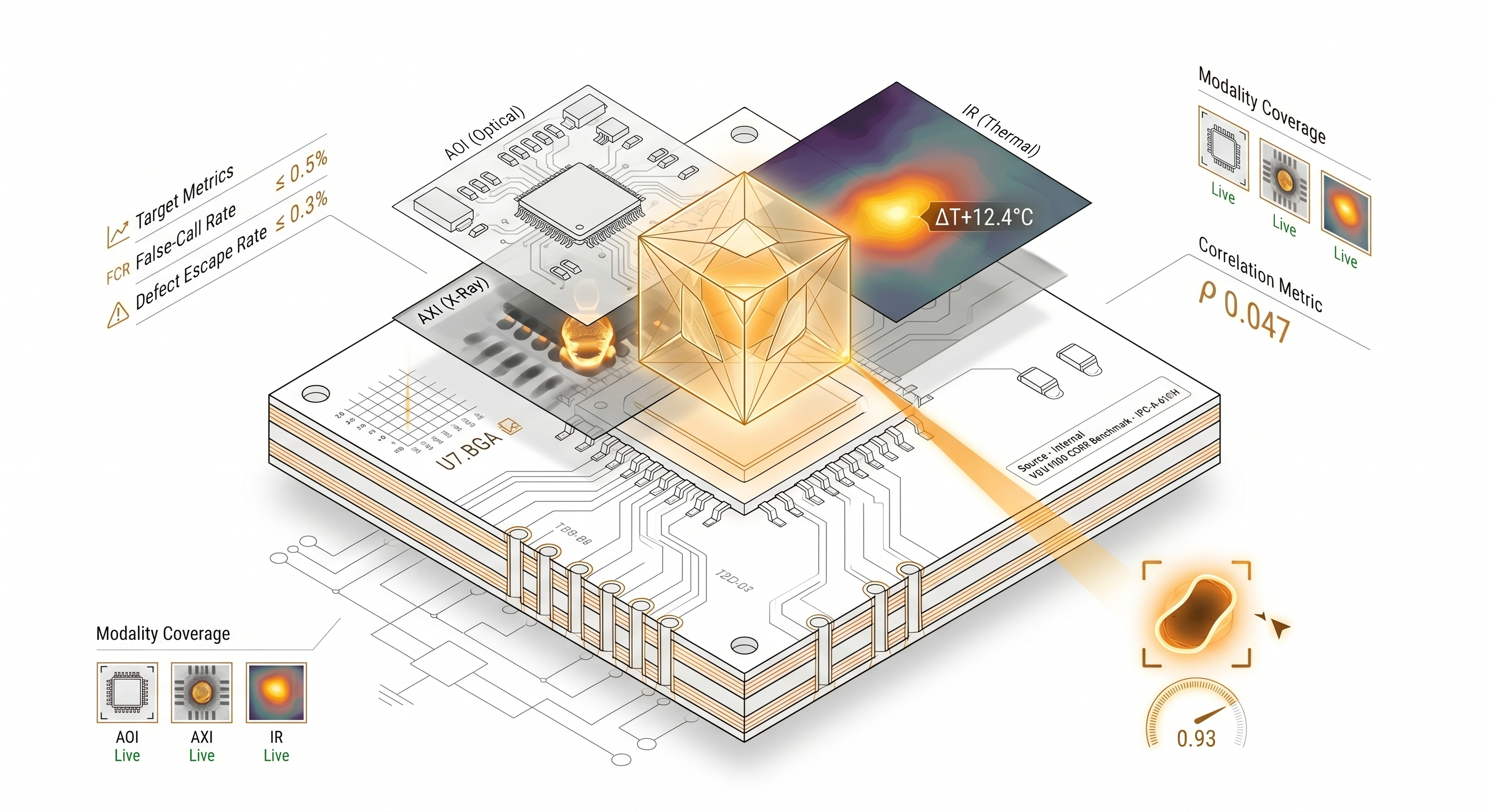

VoidSense catches failures that are invisible to any one modality by reasoning across them. Optical, X-ray, and thermal data fuse against a shared topology — a category of defect the installed base of single-modality vendors structurally cannot address.

Fusion is not a feature. It is the product.

We correlate Automated Optical Inspection, X-Ray, and thermal imagery against the same grounded topology. Disagreement between sensors is itself a signal — often the earliest and most valuable one the line will produce all week.

The only defense-grade option on the board.

The Defense Industrial Base cannot send its process data to the cloud. VoidSense runs where the work happens — on local hardware, behind the air gap, against the standards the DIB already speaks. A market most vendors are structurally disqualified from.

Local by default. Private by design. Defense-grade by standard.

Frontier reasoning, compressed to run inside a factory cell or a sealed enclosure — no round-trip, no exposure of process IP, no outside dependency. The posture that unlocks defense, aerospace, and regulated industrial budgets most cloud-first vendors will never touch.

Rare founders for a rare problem.

Two founders with 30+ combined years across agentic systems, spatial AI, and high-performance hardware — the exact intersection this category requires, and almost nobody else has.

Former Systems Lead at a frontier Reality Labs group, driving agentic self-improving systems, and previously inside a major chipmaker's AI division. Was CTO of a CG deep-tech startup acquired by a leading social-media company. A veteran of high-stakes computer vision at a Hollywood-scale visual-effects studio. 3 patents filed in distributed architecture and real-time computer vision.

Former Team Lead at a $300M agricultural-AI firm — the closest analog to our physical-AI thesis currently in-market. Technion-trained Electrical Engineer with 15 years shipping high-performance hardware at a flagship consumer-electronics company and multithreaded processor validation at a blue-chip semiconductor research lab.